Новости Компютерных технологий

"Технологическая гонка: TSMC и Samsung соревнуются в разработке инновационных методов упаковки чипов"

06/25/2024 09:17:08

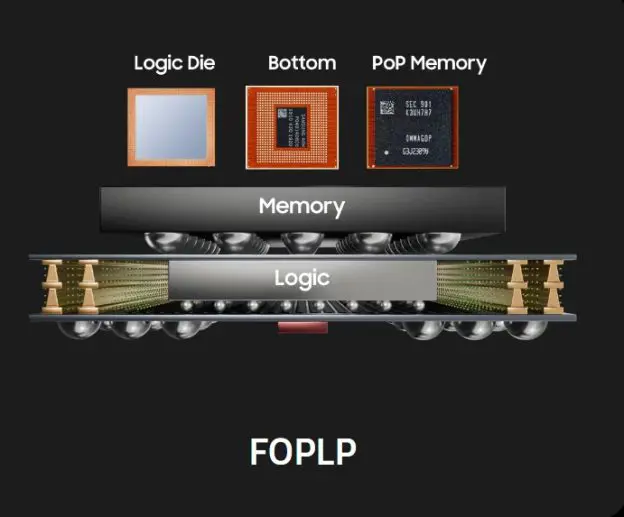

Согласно предыдущему отчету Nikkei, Taiwan Semiconductor Manufacturing Company (TSMC) выходит на рынок разветвленной упаковки на уровне панелей (FO-PLP), также известной как плоскопанельная упаковка (Fo-PLP). Это представляет собой значительный шаг вперед в технологии производства микросхем, поскольку позволяет увеличить количество чипов, которые могут быть размещены на одной подложке.

Samsung, ключевой конкурент TSMC, также активно работает над развитием этой технологии. Как сообщает Business Korea, Samsung добилась значительного прогресса в области PLP после того, как в 2019 году приобрела бизнес PLP у Samsung Electro-Mechanics.

Интересно отметить, что обе компании видят в этой технологии потенциал стать их "секретным оружием". Несколько лет назад TSMC использовала свою технологию InFO-WLP (интегрированная фольга-упаковка уровня пластины) для получения всех заказов Apple на процессоры A10. Samsung, столкнувшись с необходимостью конкурировать с TSMC, начала сотрудничество с Samsung Electro-Mechanics для разработки собственной технологии FO-PLP.

По словам Кён Ке Хёна, бывшего главы Samsung Electronics, технология PLP имеет решающее значение для отрасли. Он подчеркнул, что полупроводниковые матрицы искусственного интеллекта, которые обычно имеют размеры 600 x 600 мм или 800 x 800 мм, требуют использования таких технологий, как PLP. Samsung активно разрабатывает эту технологию и сотрудничает с клиентами. Компания предлагает передовые услуги по упаковке, включая I-Cube 2.5D упаковку, X-Cube 3D IC упаковку и 2D FOPKG упаковку. Кроме того, Samsung уже предлагает решения для приложений, требующих интеграции памяти с низким энергопотреблением, такие как разветвленная упаковка на уровне панели и разветвленная упаковка на уровне пластины.

TSMC, с другой стороны, сотрудничает с производителями оборудования и поставщиками материалов для разработки технологии упаковки на уровне панелей. Хотя исследования все еще находятся на начальном этапе, использование прямоугольной подложки вместо традиционной круглой пластины может позволить разместить на одной пластине больше чипсетов. TSMC экспериментирует с прямоугольными подложками длиной 515 мм и шириной 510 мм, обеспечивая полезную площадь более чем в три раза больше, чем у 12-дюймовой пластины.

Таким образом, участие TSMC в исследованиях PLP можно рассматривать как ответ на растущий спрос на искусственный интеллект и увеличение потребности в интеграции большего количества транзисторов и памяти в каждом чипе.